# CE439 – CAD Algorithms for Physical Design - Introduction

Christos P Sotiriou

1

CE439 - CAD Algorithms II 29/2/2016

#### Contents

- ▶ TCL Library and CAPI

- https://www.tcl.tk/

- https://www.tcl.tk/man/tcl8.5/TclLib/contents.htm

- ▶ GNU Readline API

- http://www.gnu.org/software/readline/

**>** 2

#### Recommended Texts

#### Recommended books

- S. K. Lim, *Practical Problems in VLSI Physical Design Automation*, Springer, 2008

- C. J. Alpert, D. P. Mehta, S. S. Sapatnekar, Handbook of Algorithms for Physical Design Automation, Auerbach Publications, 2008

- S. M. Sait and H. Youssef, VLSI Physical Design Automation: Theory and Practice, World Scientific, 1999.

#### Algorithm book

- ► T. H. Cormen, C. E. Leiserson, R. L. Rivest, C. Stein Introduction to Algorithms, MIT Press, 2009 (3<sup>rd</sup> edition)

- ▶ Selected papers from the literature.

3

CE439 - CAD Algorithms II 29/2/2016

## Physical Design Problems to Algorithms

| CAD Algorithms                                                              | Physical Design Stages            |

|-----------------------------------------------------------------------------|-----------------------------------|

| Graph algorithms                                                            | Partition                         |

| Graph algorithms Combinatorial Algorithms Mathematical programming (QP, LP) | Placement                         |

| Shortest path  Mathematical programming (LP)  Greedy algorithms             | Static Timing Analysis<br>Routing |

| Graph Algorithms<br>Combinatorial Algorithms                                | Legalization                      |

Identify Problem Formulation into an Algorithm

- 4

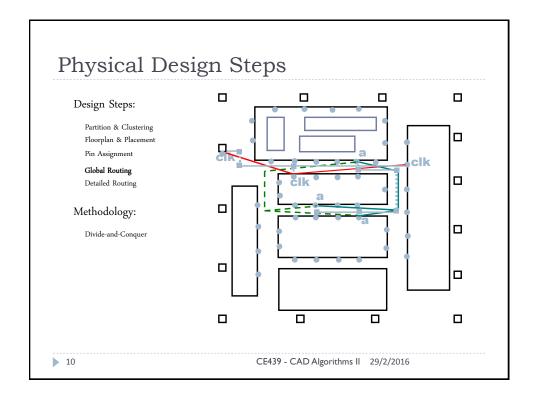

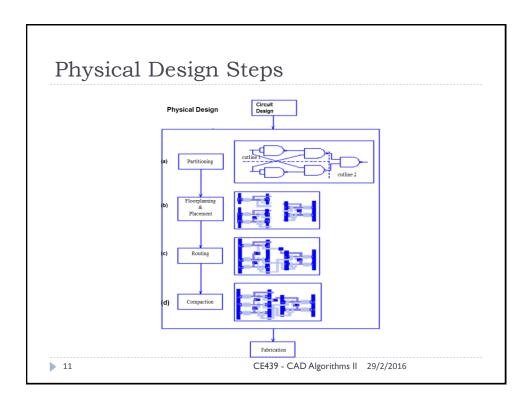

# Physical Design Steps

- ▶ Design Steps in More Detail

- ▶ Partitioning/Clustering

- Floorplanning

- I/O Pin Assignment

- ▶ Placement

- Clock Tree Synthesis

- ▶ Global Routing

- Detail Routing

9

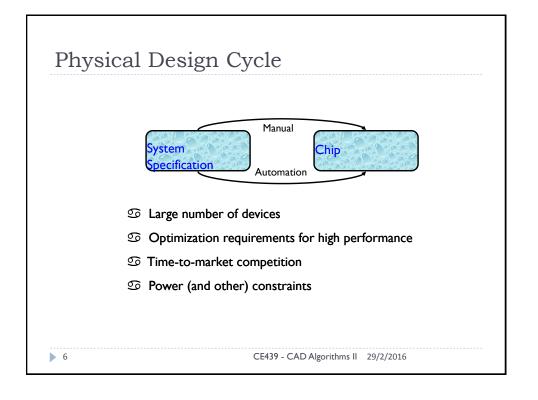

# Complexities of Physical Design

- More than 100 million transistors

- Performance driven designs

- Power-constrained designs

- ► Time-to-Market

- ▶ PPA (Power-Performance-Area) is key metric

12

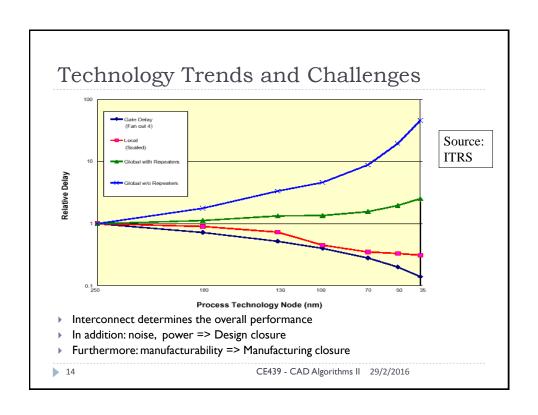

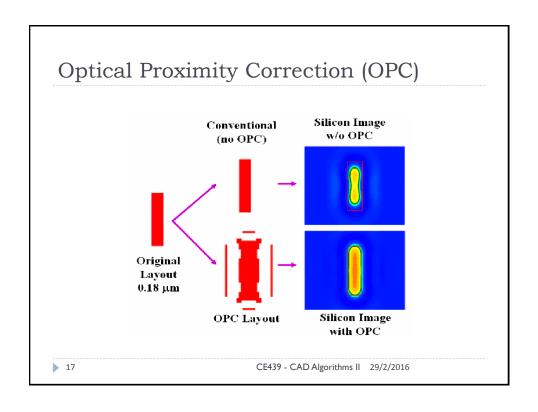

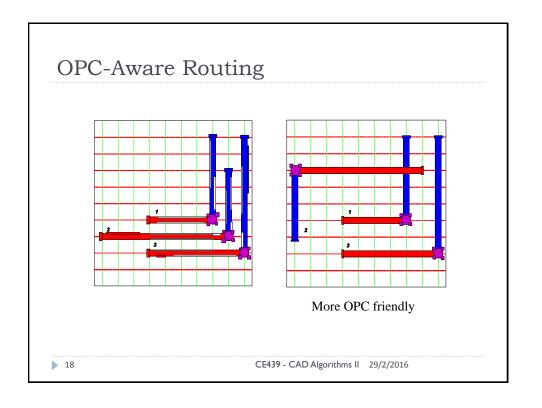

## Why is Physical Design Important?

- Many existing solutions are still very suboptimal

- ▶ E.g., placement

- Interconnect dominates

- No physical layout, no accurate interconnect

- More new physical and manufacturing effects pop up

- Crosstalk noise, ...

- ▶ OPC (manufacturability), etc.

- More vertical integration needed

- Physical design is the KEY linking step between higher level planning/optimization and lower level modeling

13

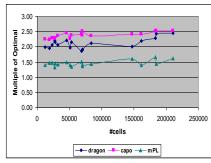

#### The Placement Problem

- Placement, to large extend, determines the overall interconnect

- If it sucks, no matter how well you interconnect optimization engine works, the design will suck

- ▶ Placement is a very old problem, but got renewed interest

- Mixed-size (large macro blocks and small standard cells)

- Dptimality study shows that placement still a bottleneck

- Not even to mention performance driven, and coupled with buffering, interconnect optimizations, and so on (all you name)

15

CE439 - CAD Algorithms II 29/2/2016

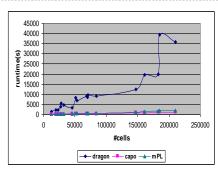

## Comparison with Optimal Solution

- ▶ Capo: Based on recursive min-cut (UCLA-UMich)

- ▶ Dragon: Recursive min-cut + SA refinement at each level (NWU-UCLA)

- ▶ mPL: multi-level placer (UCLA)

- There is significant room for improvement in placement algorithms: existing algorithms are 50-150% away from optimal!

16

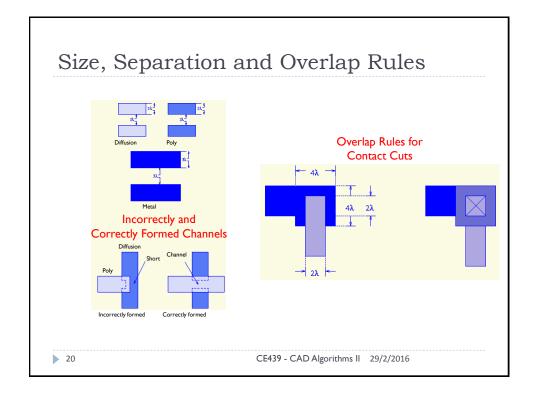

## Basic Design Rules

- ▶ I. Size Rules

- ▶ 2. Separation Rules

- ▶ 3. Overlap Rules

$\begin{array}{lll} \text{Diffusion Region Width} & 2\lambda \\ \text{Polysilicon Region Width} & 2\lambda \\ \text{Diffusion-Diffusion Spacing} & 3\lambda \\ \text{Poly-Poly Spacing} & 2\lambda \\ \text{Polysilicon Gate Extension} & 2\lambda \\ \text{Contact Extension} & \lambda \\ \text{Metal Width} & 3\lambda \\ \end{array}$

19

#### Additional Fabrication Issues

- Scaling

- Parasitic Effects

- Yield Statistics and Fabrication Costs

- Delay Computation

- ▶ Noise and Crosstalk

- ▶ Power Dissipation

24

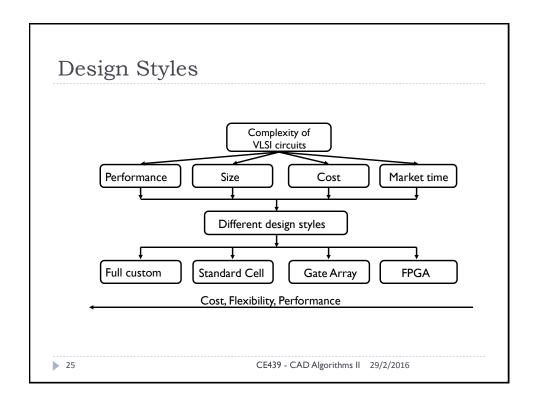

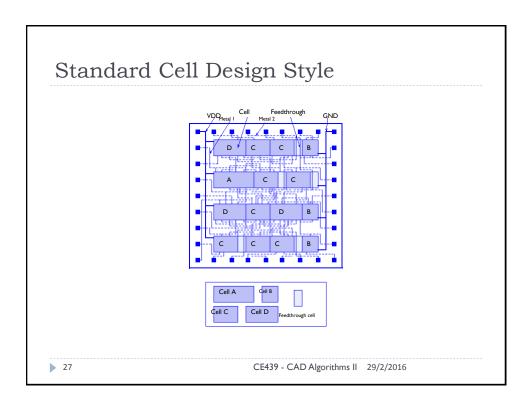

| 7-7 | gii Styi            | es  | s Con       | npariso                | on                |              |       |

|-----|---------------------|-----|-------------|------------------------|-------------------|--------------|-------|

|     |                     |     |             | st                     | yle               |              |       |

|     | İ                   | Ī   | full-custom | standard cell          | gate array        |              | FPGA  |

|     | cell size           |     | variable    | fixed height *         | fixed             | fixed        |       |

|     | cell type           |     | variable    | variable               | fixed             | programmable |       |

|     | cell placement      |     | variable    | in row                 | fixed             | fixed        |       |

|     | interconnections    |     | variable    | variable               | variable          | programmable |       |

| _   |                     | Г   |             | . 1                    |                   |              |       |

|     |                     |     |             | style                  |                   |              |       |

|     |                     | ful | ll-custom   | standard cell          | gate array        |              | FPGA  |

| L   | Area                | c   | ompact      | compact<br>to moderate | moderate          | •            | large |

| F   | Performance         | hi  | igh         | high<br>to moderate    | moderate          |              | low   |

| 1 : | abrication<br>avers | ALL |             | ALL                    | routing<br>lavers |              | none  |

## History of Physical Design Tools

| Year           | Design Tools                                                                                                                                                                                      |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1950 - 1965    | Manual Design                                                                                                                                                                                     |

| 1965 - 1975    | Layout editors<br>Automatic routers( for PCB)<br>Efficient partitioning algorithm                                                                                                                 |

| 1975 - 1985    | Automatic placement tools                                                                                                                                                                         |

|                | Well Defined phases of design of circuits                                                                                                                                                         |

|                | Significant theoretical development in all phases                                                                                                                                                 |

| 1985 – 1995    | Performance driven placement and routing tools<br>Parallel algorithms for physical design<br>Significant development in underlying graph theory<br>Combinatorial optimization problems for layout |

| 1995 – 2002    | Interconnect layout optimization, Interconnect-<br>centric design, physical-logical codesign                                                                                                      |

| 2002 - present | Physical synthesis with more vertical integration for design closure (timing, noise, power, P/G/clock, manufacturability)                                                                         |

31

CE439 - CAD Algorithms II 29/2/2016

## Algorithms

- ▶ To put devices/interconnects together into VLSI chips

- ▶ Fundamental questions: How do you do it smartly?

- ▶ Definition of algorithm in a board sense: A step-by-step procedure for solving a problem. Examples:

- Cooking a dish

- Making a phone call

- Sorting a hand of cards

- ▶ Definition for computational problem: A well-defined computational procedure that takes some value as input and produces some value as output

32

## Some Algorithm Design Techniques

- Greedy

- Divide and Conquer

- Dynamic Programming

- Network Flow

- Mathematical Programming (e.g., linear programming, integer linear programming)

33

CE439 - CAD Algorithms II 29/2/2016

#### Algorithm Analysis

- ▶ There can be many different algorithms to solve the same problem.

- ▶ Need some way to compare 2 algorithms.

- Usually run time is the most important criterion used

- > Space (memory) usage is of less concern now

- However, difficult to compare since algorithms may be implemented in different machines, use different languages, etc.

- Also, run time is input-dependent. Which input to use?

- ▶ Big-O notation is widely used for asymptotic analysis

- N→inf

34

#### **Big-O Notation**

- Consider run time for the worst input

- upper bound on run time.

- Express run time as a function input size n.

- Interested in the run time for large inputs.

- Therefore, interested in the growth rate.

- Ignore multiplicative constant.

- Ignore lower order terms.

- $\rightarrow$  3n<sup>2</sup>+6n+2.7 is O(n<sup>2</sup>).

- $\rightarrow$  n<sup>1.1</sup>+10000000000n is O(n<sup>1.1</sup>).

- ightharpoonup n<sup>1.1</sup> is also O(n<sup>2</sup>), but to be more precise, it is O(n<sup>1.1</sup>)

35

CE439 - CAD Algorithms II 29/2/2016

#### Growth Rates of Some Functions

$$O(\log n) < O(\log^2 n) < O(\sqrt{n}) < O(n)$$

$$< O(n \log n) < O(n \log^2 n) < O(n^{1.5}) < O(n^2)$$

Functions

$$O(n^3) < O(n^4)$$

$$O(n^6) = O(2^{e \log n}) \text{ for any constant } c$$

$$< O(n^{\log n}) = O(2^{\log^2 n})$$

$$< O(2^n) < O(3^n) < O(4^n)$$

$$< O(n!) < O(n^n)$$

Functions

$$C = C(n^{\log n}) = C(n^{\log n}) = C(n^{\log n})$$

$$< O(n^{\log n}) = O(n^{\log n}) = C(n^{\log n}) = C(n^{\log n})$$

> 36

#### NP-Complete Problems

- ▶ The class <u>NP-Complete</u> is the set of problems which we believe there is no polynomial time algorithms.

- ▶ Therefore, it is a class of hard problems.

- ▶ NP-Hard is another class of problems containing the class NP-Complete.

- If we know a problem is in NP-Complete or NP-Hard, there is no hope to solve it efficiently.

37

CE439 - CAD Algorithms II 29/2/2016

### Algorithm Solution Types

- Polynomial time algorithms

- Exponential time algorithms

- Special case algorithms

- Approximate algorithms

- ▶ Heuristic algorithms

38